Изучаем особенности DDR5 до старта массовых продаж

В связи со скорым выходом нового вида DDR5 SDRAM (double-data-rate five synchronous dynamic random access memory) появляется всё больше информации о данном виде оперативной памяти, поэтому посмотрим на всё, что известно о ней на данный момент. Начнём с не самой значительной для многих информацией, но в тоже время достаточно важной.

Заранее остановимся на одном определении, чтобы в дальнейшем понимать о чём идёт речь. Банк памяти (memory bank) — логическая единица хранения, которая применяется в электронике и зависит от используемого оборудования. В компьютерном железе банк памяти может определять контроллером памяти вместе с физической организацией слотов памяти. В типичной синхронной динамической со случайным доступом памяти (SDRAM) или в синхронной динамической со случайным доступом памяти с удвоенной скоростью передачи данных (DDR SDRAM) банк состоит из нескольких строк и столбцов, включающих в себя блоки хранения, которые распределяются по нескольким микросхемам. В одиночной операции чтения или записи доступ осуществляется только к одному банку, поэтому количество битов в столбце или строке для каждого банка и чипа равно ширине шины памяти в битах (одноканал). Размер банка определяется дополнительно количеством битов в столбце и строке в каждом из чипов умноженном на количество чипов в банке.

Также хотелось бы уточнить, что материал достаточно сложный, но это не значит, что он недоступный для всех. Воспринимать стоит следующим образом: если вы понимаете в оперативной памяти чуть больше, чем на уровне одноранга/двуранга, объема памяти, основных напряжений, то можно прочитать статью целиком, в ином случае рекомендуется останавливаться только на интересующих разделах.

Габаритные размеры

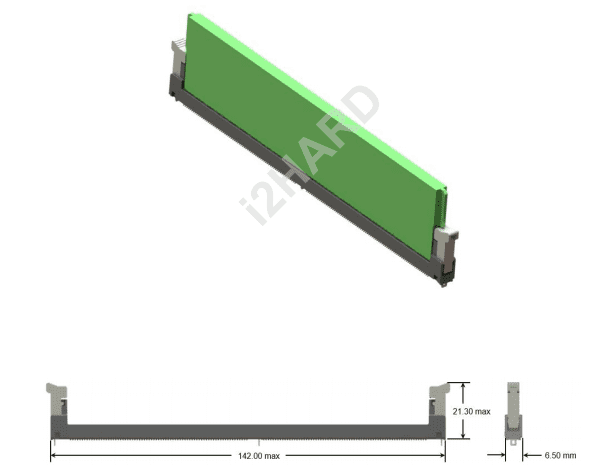

Начнём с габаритных разъёмов. Есть ли какие-либо изменения со стороны самого разъёма?

По данным размерам можно сказать лишь то, что это копия разъёма DDR4 без каких-либо изменений: те же 142 мм в длину, 21.3 мм в высоту и 6.5 мм в ширину.

Теперь посмотрим на саму оперативную память. В длину она имеет размеры 133.35 мм с допуском в 0.15 мм. Для дальнейшего пояснения необходимо понимать, что значит данный допуск. Размер оперативной памяти в длину 133.35 мм с учётом допуска размер может быть как 133.5 мм, так и 133.2 мм. Кроме этого допуски есть на высоту при размере 31.25 мм, допуск +0.55 мм и 0.15 мм. Ширина равна 1.27 с допуском в 0.10 мм. По длине контактов допуска нет они строго равны 62.90 мм и 57.80 мм. Также нет допуска у своеобразного перехода на линии контактов 0.50 мм.

Хорошо, размеры в целом ясны. Но что это значит для конечного пользователя "в сравнении с DDR4"? Длина, высота, толщина с учётом допусков абсолютно идентична DDR4, а вот с контактами история несколько иная. На DDR4 размеры слева направо равны 64.6 и 56.10, а у DDR5 - 62.90 и 57.80. В итоге разница порядка 1.5 мм в меньшую сторону и 1.7 мм в большую сторону. С учётом нахождения ключа между контактами на оперативной памяти нас ждёт в целом 1 в 1 по размеру память, что и DDR4. Если с переходом от DDR3 к DDR4 мы бы не смогли поставить одну память вместо другой, то теперь некоторые особо упорные пользователи смогут. Для того, кто привык подбирать память по разъему, будет достаточно критично, а для незнающих людей может стать некоторой проблемой.

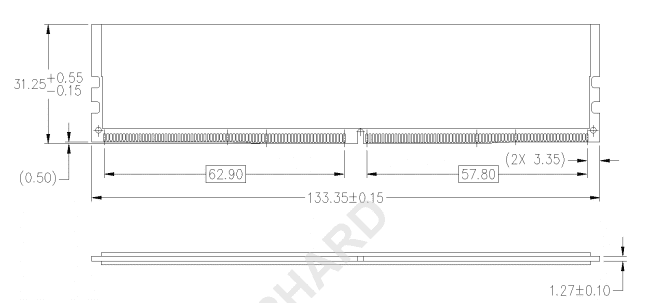

Хорошо, а почему размеры первой и второй групп контактов изменились? Если быть конкретнее, то их положение. На самом деле это произошло не просто так.

Если обратиться к DDR4, то расположение контактов было следующее:

Запоминаем в уме данную таблицу и теперь смотрим на таблицу с DDR5:

Самое очевидное, что можно заметить, так это то, что строка KEY больше в первом случае, чем во втором. Также вы видите, что количество контактов осталось точно на таком же уровне, а именно 288. Многие уже успели заметить, что 76 и 220 контакты «уехали» во вторую группу. Тем самым в ней теперь на пару контактов больше, чем в первой.

Стоит уточнить, что пара контактов имеется в виду с учётом их двустороннего расположения. Если же смотреть с каждой стороны по отдельности, то произошло смещение на 1 контакт с одной стороны и на 1 с другой.

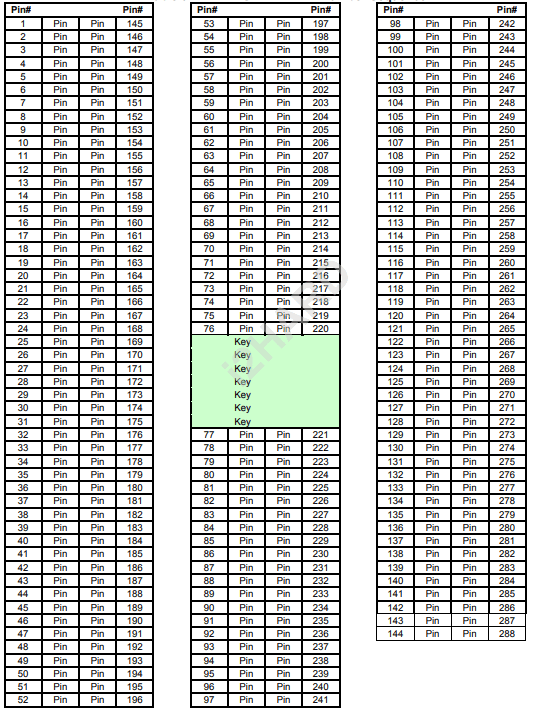

Пропускная способность

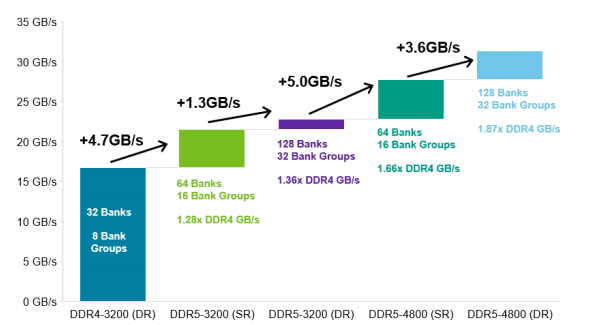

Если начать говорить о DDR4, то она разрабатывалась в первую очередь с прицелом на снижение энергопотребления и была направлена в большую степень для применения в каких-либо мобильных устройствах или дата-центрах. DDR5 же, напротив, ориентирована в большей степени на пропускную способность. Если сравнить DDR4 на скорости передачи данных равной 3200 MT/s (транзакций в секунду) и DDR5 на аналогичной частоте, то получится увеличение пропускной способности в 1.36 раза. Говоря о нижнем пороге скорости передачи данных DDR5, отметим, что теперь она равна 4800 MT/s, что больше в 1.87 раза, чем у DDR4-3200.

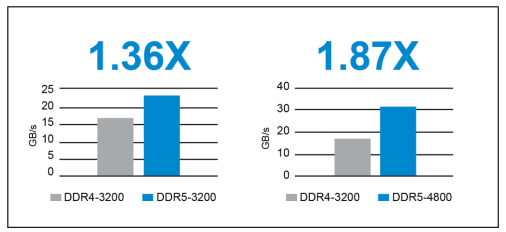

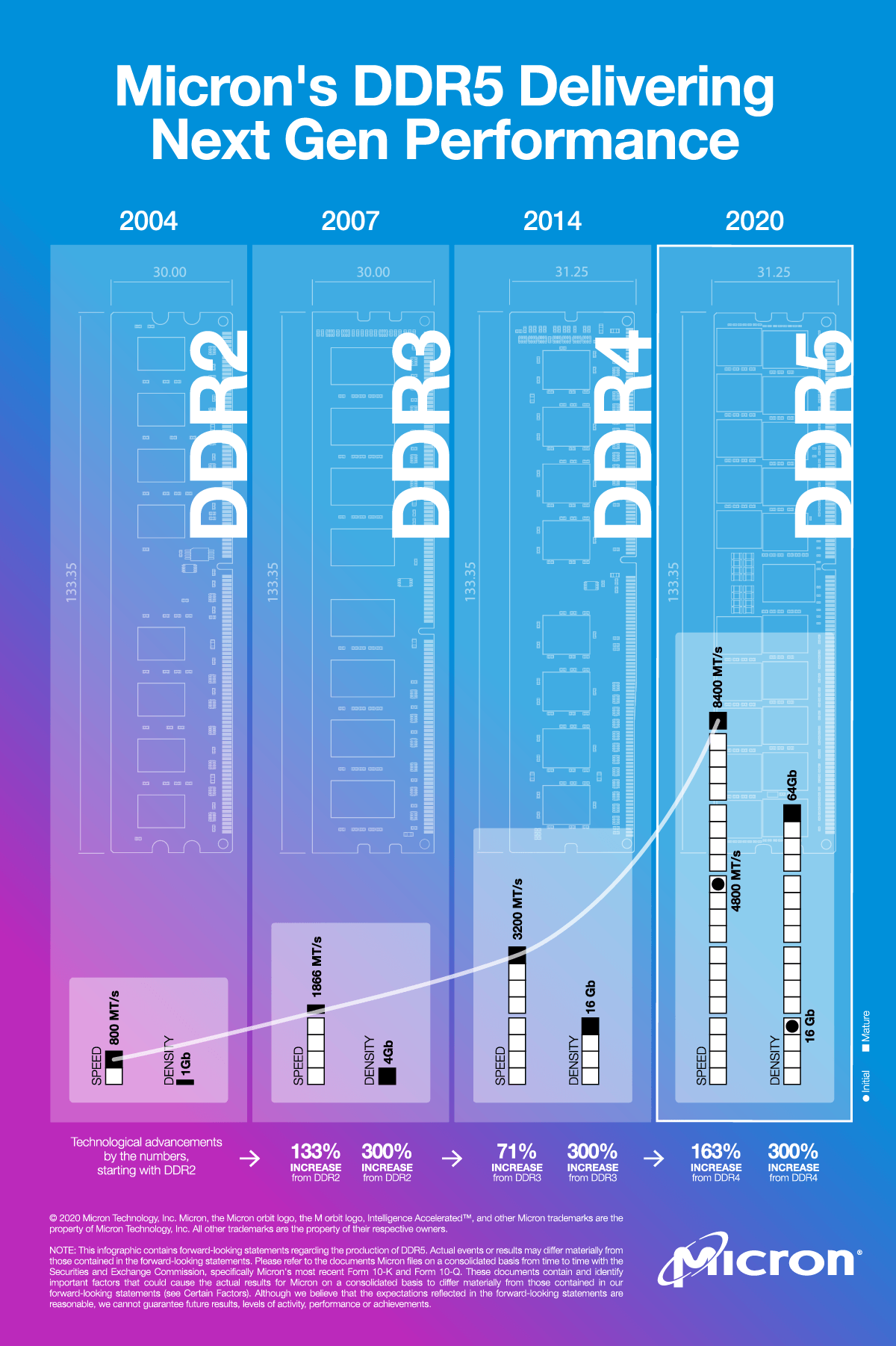

Инфографика Micron

Один из крупнейших производителей чипов для оперативной памяти поделился своеобразной инфографикой.

Как можно видеть, показана инфографика, начиная с DDR2 и по новое поколение DDR5. Сверху указаны годы, когда оперативная память была выпущена. Странно, но на пороге 2021 года нет соответствующей памяти. На самом деле первая оперативная память действительно была выпущена в 2020 году, но пока не для массового, а коммерческого использования.

Далее, если мы посмотрим ниже, то увидим скорость (speed), емкость (density) и своеобразный график, который связан с точками скоростей передачи данных 800, 1866, 3200, 8400 транзакций в секунду. Судя по графику, прирост от DDR2 до DDR4 был достаточно линейным, в тоже время с переходом от DDR4 к DDR5 график резко подскочил вверх. Кроме этого, можно увидеть, что нижнее значение емкости оперативной памяти на DDR5 будет составлять 16 Гб, а максимальное - 64 Гб. Как пишет производитель, скорость передачи данных увеличилась на 163 %, а емкость - на 300 %. Естественно, в учёт берутся только максимальные значения и они указаны с учётом стандарта JEDEC. Кроме этого оперативная память DDR4 по XMP давно уже перешла отметку в 3200, а DDR5 только выйдет на массовый рынок, поэтому какой будет потолок для DDR5 в будущем, пока остаётся под вопросом.

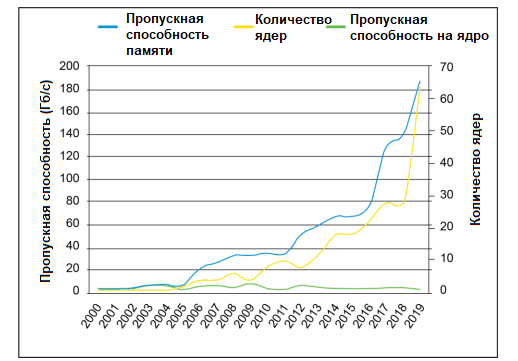

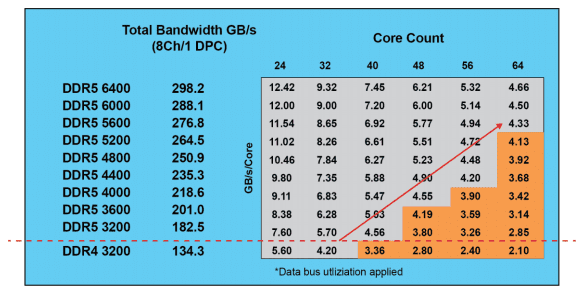

Пропускная способность на ядро

Производительность в той или иной степени увеличивается из года в год, растут частоты, количество операций за такт. Становится больше сложность в осуществлении передачи сигналов, подачи постоянного питания, кроме этого увеличивается количество ядер. Одной из причин появления DDR5 стало то, что пропускная способность памяти росла, количество ядер увеличивалось соизмеримо, но при этом пропускная способность на ядро в целом оставалась на одном и том же уровне из года в год. К тому же в последнее время она даже начала падать, поэтому уже достаточно не редки случаи, когда процессорная производительность упирается в подсистему памяти.

Особенности DDR5

Увеличенная скорость передачи данных

На картинке ниже можно увидеть суммарную пропускную способность (Total Bandwidth) в Гб/с (8 канальный режим) на разных частотах, справа указано количество ядер (Core Count) и пропускная способность на ядро. К примеру, пропускная способность на ядро DDR4 3200 при 32 ядрах равна 4.20 ГБ/с. С количеством ядер равным 64 для сохранения аналогичной производительности необходима память DDR5 5600.

Особенности протокола для повышения производительности

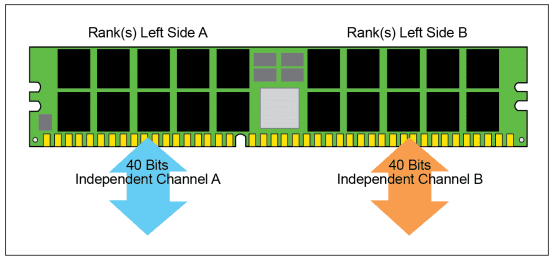

Кроме более высоких скоростей передачи данных и улучшений схемы ввода-вывода, DDR5 представила новый протокол, который не зависит от передачи данных, связанной с увеличением пропускной способности и производительности. Для примера, у DDR5 два 40-битных (32 бита плюс ECC) независимых канала. В сочетании с новой увеличенной длиной пакета по умолчанию равной 16 (BL16), как компонента DDR5, это позволяет одному пакету получить доступ к 64 Б данных (стандартный размер линейного кеша ЦП), используя только один из независимых каналов или только половину от всей DIMM. Благодаря этой возможности чередование доступа к двум каналам позволяет значительно улучшить параллельную работу. Грубо говоря, 8-канальная система превращается в 16-канальную.

В массиве данных DRAM количество групп банков (BG) в DDR5 увеличивается вдвое по сравнению с DDR4. Данное улучшение позволяет контролеру избежать снижения производительности, связанного с последовательным доступом к памяти в пределах одних и тех же банков (например, это приводит к тому, что tCCD_S становится ограничением последовательного доступа и выполняется значительно дольше, чем tCCD_L). Добавление данных обновлений и улучшение пре/постамблей на командную шину (путем введения интегратора) помогает смягчить традиционные узкие места производительности, обычно наблюдаемые в DDR4, улучшая общую эффективную пропускную способность интерфейса памяти.

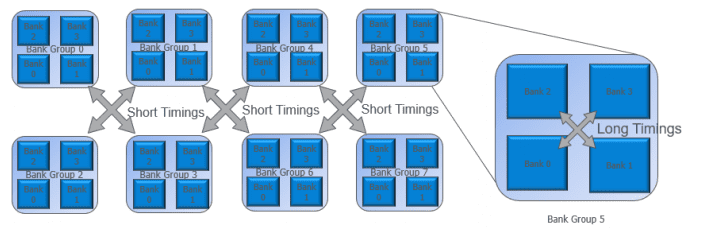

Увеличение общего количество банков

При увеличении емкости памяти необходимо увеличивать количество банков. Как уже говорилось выше, количество групп банков удваивается, при этом количество банков на одну группу остаётся одинаковым. Доступы с чередованием по времени от банка к группе банков короче, чем доступ от банка к банку в рамках доступа к конкретной группе банков. У данных параметров таймингов «длинные» (Long timings) (tCCD_L, tWTR_L, tRRD_L) и «короткие» (Short timings) (tCCD_S, tWTR_S, tRRD_S) тайминги синхронизации. Длинные относятся к типу от банка к банку, в то время как короткие тайминги - к доступу к группам различных банков.

Увеличение числа групп банков смягчает внутренние временные ограничения, увеличивая вероятность того, что короткие тайминги уже используются.

Команды обновления (REFRESH)

В дополнение к стандартной команде ALL-BANK REFRESH (REFab), доступной в DDR5 и более ранних версиях DDR SDRAM, в DDR5 появляется ещё одна - SAME-BANK REFRESH (REFsb). Команда REFsb нацелена на тот же банк во всей группе банков, определяясь битами банка через биты команд/адреса при выдаче команды REFsb. Команда обновления на устройствах SDRAM требуют, чтобы банки, которые готовятся к обновлению, были в состоянии простоя (предварительно заряжены, но активность данных на них отсутствует) до выдачи команды и банки не могли возобновить последующую активность записи и чтения в течение команды обновления (тайминг tRFC). Команды обновления выдаются со средним периодическим интервалом (тайминг tREFI). Для команд REFab система должна гарантировать, что все банки находятся в состоянии простоя, прежде чем подавать команду, в среднем - один раз в 3.9 мкс в «нормальном» режиме обновления с длительностью 295 нс для 16 Гб DDR5 SDRAM.

Преимущество REFsb с точки зрения производительность заключается в том, что только один банк в каждой группе должен быть в состоянии простоя перед выдачей команды. Оставшиеся 12 банков (для 16 Гб, x4/x8 устроств, синие ячейки на картинке ниже) не должны находиться в режиме ожидания при подаче команды REFsb, при этом единственное ограничение тайминга для необновляемых банков заключается в запуске задержки обновления одного и того же банка (тайминг tREFSBRD).

Команды REFsb могут быть выполнены только в режиме обновления с высокой степенью детализации (FGR). Таким образом каждый банк должен получать команду обновления в среднем каждые 1.95 мкс. Длительность REFsb составляет 130 нс для 16 Гб DDR5 SDRAM, что также снижает блокировку доступа к системе (tRFCsb) для обновляющихся в текущий момент банков (красные ячейки на картинке выше). Ограничение при использовании команды REFsb состоит в том, что каждый( «один и тот же банк») будет вызван второй командой REFsb, но команды REFsb могут быть получены в любой для банков последовательности.

В зависимости от соотношения команд записи и чтения симуляция показывает, что производительность системы увеличивается от 6 до 9 процентов при использовании REFsb по сравнению с REFab, как показано ниже для операции чтения.

|

Средняя задержка при обновлении |

|

|

REFab |

11.2 нс |

|

REFsb |

5 нс |

Улучшение производительности

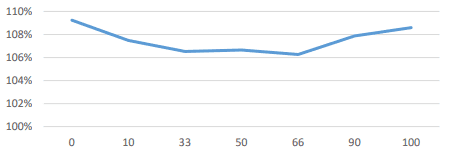

Используя особенности, которые были указаны выше (увеличение вдвое количества банков и групп банков, BL16 и обновление одного и того же банка), симуляция рабочей нагрузки с произвольным доступом в 64 Б показывает, что достигается существенное повышение производительности по сравнению с двухранговыми модулями DDR4 со скоростью 3200 MT/s, как показано ниже. В данном сценарии рассмотрено 8 каналов на 1 систему.

График нормализован относительно случайного доступа 64 Б, 66 % чтения, x4 симуляция 16 Гб. DR – двуранг, SR – одноранг, Banks – Банки, Bank Groups – группы банков. Также на графике показано увеличение пропускной способности относительно DDR4-3200.

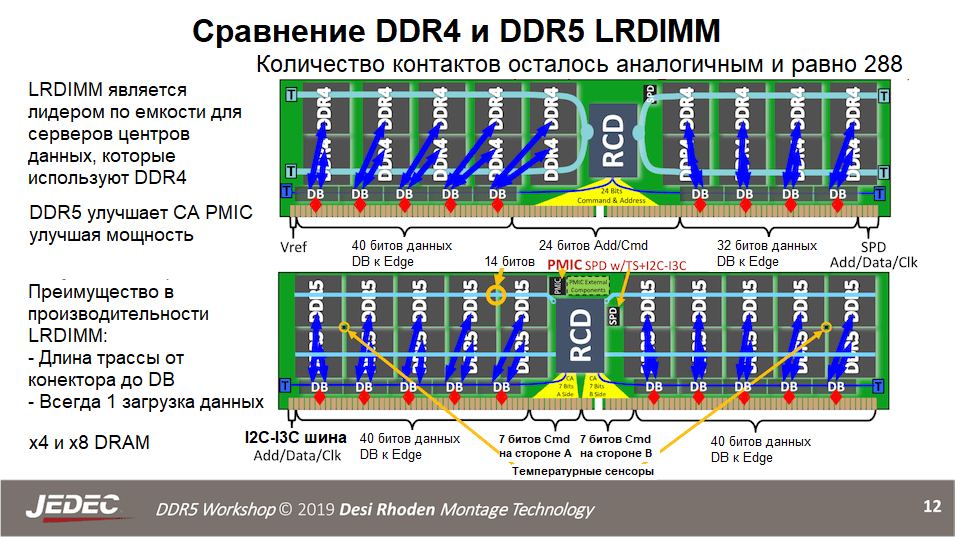

Сравнение памяти LRDIMM

Если смотреть достаточно просто на изменения оперативной памяти, то мы видим, что чипов стало немного больше. Если DDR4 имеет по 10 чипов слева и только 8 справа, то у DDR5 их количество равно друг другу. Кроме этого появились два температурных сенсора. Конечно, сенсоры есть и сейчас в некоторых планках оперативной памяти. Число битов данных стало равно друг другу со стороны A и B, а также расположение чипов со стороны A стало немного ближе к DB, чем на DDR4. Также можно увидеть, что шина для стороны A или стороны B общая, в то время, как у DDR5 различна. Число битов команд и адресов у DDR4 общее и составляет 24, а у DDR 5 различное для каждой из сторон и равно 7.

Доступная в продаже память

На текущий момент в продаже уже имеется память от Teamgroup с таймингами CL40-40-40-77 1.1 В, частотой 4800 МГц и объемом 2x16 Гб.

Многие уже скорее всего заметили, что чипов всего 4. Судя по живым фотографиям, с другой стороны они отсутствуют, а это означает, что 1 чип равен 4 Гб, в итоге набирается 16 Гб, при этом задействована только одна сторона B.

Teamgroup также показала модуль на 32 Гб с аналогичными таймингами и частотой. Здесь уже видно 8 чипов по 4 Гб каждый.

Сравнительная таблица DDR4 и DDR5

Теперь перейдем к сравнительной таблице с описанием особенностей и улучшением для каждой.

| Особенности | DDR4 | DDR5 | Улучшение |

| Передача данных | 1600-3200 MT/s | 4800-8400 MT/s | Увеличена производительность и пропускная способность. |

| VDD/VDDQ/VPP | 1.2/1.2/2.5 | 1.1/1.1/1.8 | Уменьшено потребление. |

| Внутренний VREF | VREFDQ | VREFDQ, VREFCA, VREFCS | Внутренние шины VREFCA / CS значительно улучшают запас по напряжению для этих контактов, обеспечивая более высокую скорость передачи данных. Это может сэкономить затраты на BOM, устраняя необходимость во внешнем опорном напряжении на плате. |

| Емкость | 2Гб-16Гб | 8Гб-64Гб | Более крупные планки оперативной памяти |

| Предварительная выборка | 8n | 16n | Обеспечивает более высокую скорость передачи данных при сохранении внутреннего диапазона частот аналогичного DDR4. |

| Эквалайзер приемника DQ | Отсутствует | Многоканальный DFE | Открывает DQ данные внутри DRAM, прямой доступ к данным на высокой скорости. |

| Регулировка рабочего цикла (DCA) | Отсутствует | DQS и DQ |

Позволяет контроллеру компенсировать искажение рабочего цикла (DCD) на всех выводах DQS и DQ путем регулировка рабочего цикла внутри DRAM. |

| Внутренний мониторинг задержки DQS | Отсутствует | Генератор интервалов DQS | Предоставляет контроллеру метод решить если / когда повторно обучать на основе изменений в DRAM задержки, вызванные перепадами напряжения и температуры; обеспечивает устойчивость к изменениям окружающей среды. |

| ECC | Отсутствует | 128б+8б SEC, проверка ошибок и очистка | Усиливает встроенную в микросхему RAS; снижает нагрузку на контроллер. |

| CRC | Запись | Чтение/Запись | Усиливает систему RAS, защищая прочитанные данные. |

| Группы банков (BG) / банки | 4 BG x 4 банков |

8 BG x 2 банка (8Гб x4/x8) 4 BG x 2 банка (8Гб x16) 8 BG x 4 банка (16-64Гб x4/x8) 4 BG x 4 банка (16-64Гб x16) |

Помогает избежать снижения производительности из-за последовательного доступа к памяти одного и того же банка. |

| Интерфейс команд/адресов | ODT, CKE, ACT, RAS, CAS, WE, A | CA<13:0> | Необходимо два цикла для некоторых (но не всех) команд, что значительно снижает количество контактов CA. |

| ODT | CA<13:0> | DQ, DQS, DM, CA шины | CA ODT обеспечивает улучшенную целостность сигнала и экономит затраты на BOM за счет устранения сети внешних согласующих резисторов для шины CA. |

| Длина пакета | BL8 (и BL4) | BL16, BL32 (и BC8 OTF, BL32 OTF) | В сочетании с 2-канальной архитектурой DIMM обеспечивает выборку строки из кэша размером 64 Б, используя только половину DIMM. |

| MIR («зеркальный» контакт) | Отсутствует | Присутствует | Улучшает сигнализацию DIMM, позволяя использовать более короткие дорожки / заглушки для модулей и дизайна плат. |

| Инверсия шины | Инверсия шины данных (DBI) | Инверсия команд/адресов (CAI) | Снижает мощность и шум на шине VDDQ. |

| CA обучение, CS обучение, режим выравнивания тренировки записи | Режим выравнивания тренировки чтения | CA тренировка, CS тренировка и режим выравнивания тренировки чтения | Увеличенный запас тайминга на выводах CA и CS обеспечивает более высокую скорость передачи данных. Обучение выравниванию записи в DDR5 также компенсирует путь DQ-DQS, упрощающий поддержку высоких скоростей передачи данных с короткими преамбулами записи и обеспечивающий более короткие циклы переключения шины. |

| Чтение шаблонов тренировок | Возможно с MPR | Выделенные MR для последовательных (определяемых пользователем), тактовых и генерируемых LFSR тренировочных шаблонов | Выделенная тренировка чтения включает MR для выбора шаблона тренировки, в том числе тот, который использует LFSR для обеспечения шаблона PRBS. Это помогает обеспечить более надежный запас тайминга на чтение, особенно при более высоких скоростях передачи данных. |

| Регистры режима | 7 x 17 битов | До 256 x 8 битов (LPDDR тип чтение/запись) | Возможности для расширения по мере необходимости для поддержки и улучшений новых функций. |

| Команды PRECHARGE | Все банки и по одному банку | Все банки, по одному банку и случайный банк | SAME BANK PRECHARGE (PREsb) позволяет предварительно заряжать определенный банк в каждой группе банков, сохраняя активное состояние всех остальных банков без изменений. |

| Команды REFRESH | Все банки | Все банки и случайный банк | SAME BANK REFRESH (REFsb) позволяет обновлять конкретный банк в каждой группе банков, сохраняя доступ ко всем другим банкам в группе банков. |

| Режим петли | Отсутствует | Присутствует | Позволяет тестировать сигнализацию DQ и DQS между контроллером и DRAM, изолируя фактический массив памяти, поскольку доступ для чтения / записи не требуется. |

Подводя итог хочется отметить, что изменений сделано достаточно много и это даже в некоторой степени пугает. Несмотря на всё, изменения выглядят достаточно интересными, но есть определенные опасения, что стоимость памяти на старте массовых продаж будет достаточно высокой и мы получим некоторые проблемы при работе с ней в течении некоторого времени. Нам же остаётся дождаться материнских плат и процессоров с поддержкой нового вида оперативной памяти и на себе оценить важность всех произведённых изменений.

Материал подготовлен с использованием документов с сайтов micron и jedec.