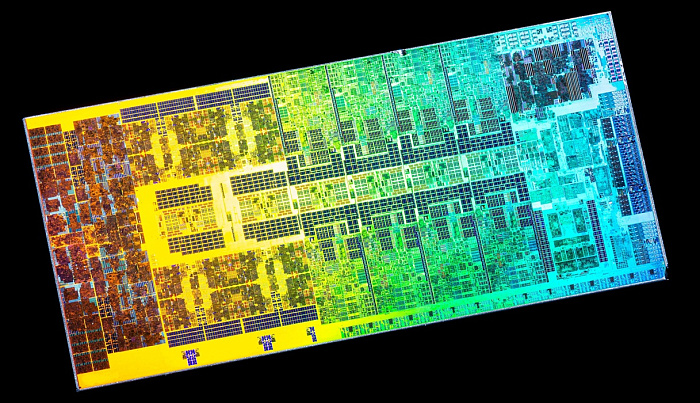

2-нм техпроцесс от TSMC предложит серьезные улучшения плотности SRAM

Современные производители полупроводников столкнулись с проблемой масштабирования памяти SRAM внутри кристаллов, из-за чего мы можем наблюдать повышение плотности размещения транзисторов в случае логики, но занимаемая памятью площадь не меняется и с каждым техпроцессом занимает все больше места.

К счастью для проектировщиков полупроводников, 2-нм технологический процесс от TSMC сможет предложить существенное улучшение масштабирования SRAM, повысив плотность размещения с 0.021 до 0.0175 µm^2, благодаря чему память будет занимать значительно меньше места в кристалле.

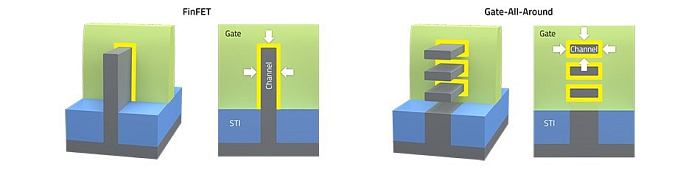

Предполагается, что такого улучшения получится добиться за счет перехода на современные транзисторы GAAFET, способные не только повысить плотность размещения транзисторов, но и снизить энергопотребление, а также положительно повлиять на производительность: сейчас TSMC прогнозирует 15% повышение плотности транзисторов, 30% повышение энергоэффективности и 15% повышение производительности по сравнению с N3E.