TSMC столкнулась с проблемой масштабирования SRAM

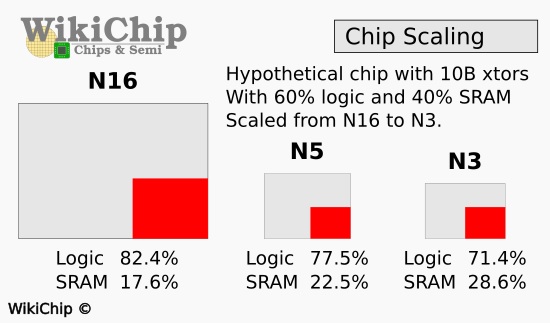

3-нм технологический процесс TSMC обещает существенно улучшить энергоэффективность и плотность размещения транзисторов. Проблема лишь в том, что эти изменения коснутся логики, в то время как ситуация с SRAM практически не изменится.

Большой кэш негативно влияет на стоимость изделий, ведь чем больше кристалл с использованием самой современной технологической нормы, тем он дороже в производстве. Это одна из причин, почему AMD предпочла использовать чиплетный дизайн в случае игровых видеокарт нового поколения, в которых кристалл логики и кристаллы памяти изготавливаются по отличающимся техпроцессам.

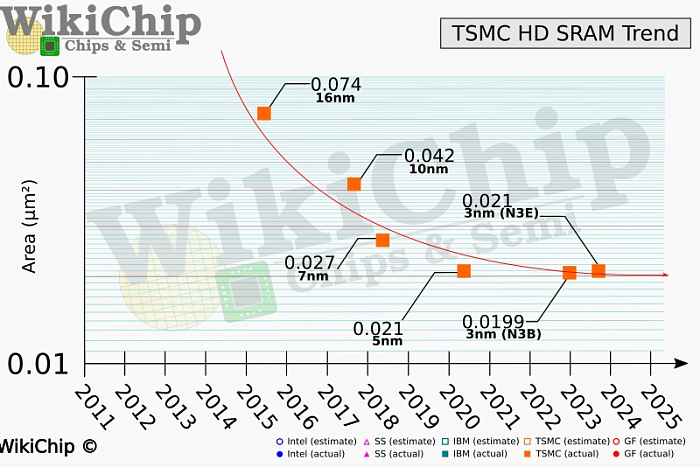

Что касается конкретно TSMC, она опубликовала статью про технологический процесс N3 в рамках International Electron Devices Meeting 2022, подсказывающую, что применение нового техпроцесса позволит увеличить плотность логики до 70%, в то время как плотность SRAM увеличится с 0.021 мкм² до 0.0199 мкм² (N3B), то есть всего на 5%, а приход N3E и вовсе вернет 0.021 мкм², что означает полное отсутствие масштабирования по сравнению с N5.

Подводя итог, несмотря на то, что современные и будущие технологические нормы позволяют существенно улучшить плотность логики, они не способны улучшить плотность SRAM, из-за чего стоимость монолитных кристаллов будет увеличиваться, а чиплетный дизайн, с применением различных техпроцессов для удешевления производства, будет набирать актуальность.