AMD, Intel, TSMC и другие объединились и создали единый стандарт соединения чиплетов

Многие производители и проектировщики полупроводниковой продукции давно начали переходить на использование чиплетного или плиточного дизайна в своих изделиях. Проблема такого подхода заключается в том, что каждая компания использует свои технологии для соединения нескольких чиплетов, что делает невозможным объединение различных блоков разных производителей.

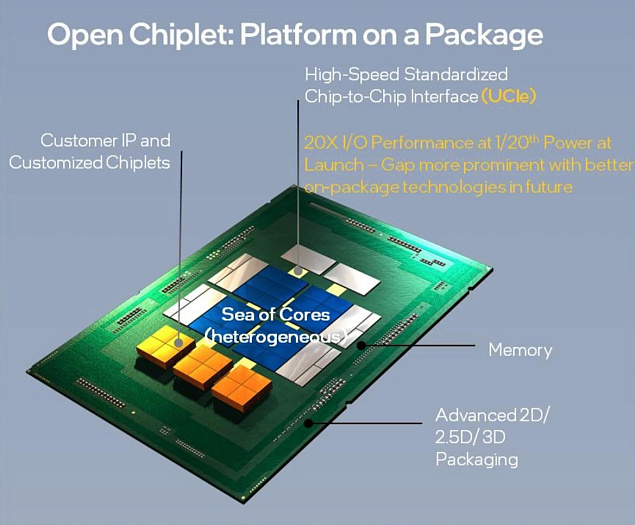

Эту проблему давно поняли крупные полупроводниковые компании, в связи с чем создали консорциум для создания единого стандарта соединения чиплетов Universal Chiplet Interconnect Express (UCIe). Совместной разработкой стандарта занимались Advanced Semiconductor Engineering, AMD, ARM, Google, Intel, Meta, Microsoft, Qualcomm, Samsung и TSMC.

Стандарт подразумевает использование единого логического и аппаратного интерконнекта для соединения чиплетов и опирается на зарекомендовавшие себя в отрасли стандарты PCI Express и Compute Express Link. UCIe 1.0 может работать только с 2D и 2.5D-упаковками, но в будущем планируется добавление работы и с 3D-упаковками.

На текущий момент UCIe 1.0 имеет следующие характеристики: скорость передачи данных до 32 GT/s, ширина шины 16 или 64 бит, плотность соединений 100-130 или 25-55 мкм (расстояние между контактами) и задержку менее 2 нс. С остальными характеристиками можно ознакомиться в представленной таблице. Следует отметить, что стандарт подразумевает использование “Стандартной” и “Расширенной” упаковки.

Консорциум стандарта Universal Chiplet Interconnect Express открыт для всех желающих и в него могут вступить любые компании, которые сочтут в этом необходимость. Например, в нем отсутствует NVIDIA и у неё есть возможность вступить в него, если появится желание.